Les semi-conducteurs de puissance contiennent des puces nues qui doivent être caractérisées avant d’être intégrées dans un boîtier ou un module de puissance, mais plusieurs défis doivent d’abord être surmontés.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat exclusif de contenu numérique avec Bodo’s Power Systems.

Les dispositifs semi-conducteurs de puissance sont utilisés sous diverses formes—emballés en dispositifs montés en surface (SMD) ou en modules de puissance—dans une gamme d’applications. Les semi-conducteurs de puissance contiennent des puces nues qui doivent être caractérisées avant d’être intégrées dans un boîtier ou un module de puissance afin d’accélérer le développement. Cependant, la petite taille, la structure fragile et les effets parasites causés par le sondage créent plusieurs défis à relever.

Les dispositifs semi-conducteurs de puissance sont d’abord fabriqués sur un wafer, suivis de leur découpe et de leur emballage avant d’être utilisés dans de réels circuits électroniques de puissance. La caractérisation lors des premières phases du processus de fabrication aide à accélérer le développement des dispositifs. Pour les ingénieurs développant des modules de puissance, comprendre le comportement des puces nues de semi-conducteurs de puissance est bénéfique pour accélérer le développement et faciliter le dépannage.

Défis de la caractérisation dynamique des puces nues de semi-conducteurs de puissance

La caractérisation statique des puces nues de semi-conducteurs de puissance n’est pas trop difficile. La puce est physiquement fixée fermement sur une plateforme conductrice pour le contact de drain, et la source ainsi que la porte sont sondées à l’aide d’aiguilles depuis le dessus de la puce. Les parasites associés à la fixation ne détériorent pas significativement la performance de mesure. Des instruments tels que des traceurs de courbes ou des analyseurs d’impédance peuvent être utilisés pour la caractérisation statique.

En revanche, la caractérisation dynamique des puces nues de semi-conducteurs de puissance est extrêmement difficile. Tout d’abord, les parasites dans le circuit de test détériorent considérablement la caractérisation dynamique, notamment pour les semi-conducteurs de puissance à large bande passante en raison de leur vitesse rapide. Par exemple, les aiguilles de sondage introduisent des parasites supplémentaires, provoquant des oscillations et des résonances, ce qui conduit à des formes d’onde de mesure déformées. Ces aiguilles de sondage peuvent risquer des arcs électriques en raison des signaux de haute tension utilisés lors des tests.

Les MOSFET SiC, les dispositifs GaN verticaux, les MOSFET Si et les IGBTs présentent une structure de dispositif verticale où le courant circule du haut de la puce vers le bas. Sonde une puce par le haut et le bas est extrêmement délicat. Par conséquent, un côté de la puce doit être soudé. Cependant, souder et déssouder la puce à une PCA est peu pratique et accélère l’usure de la carte, la rendant moins idéale pour les tests.

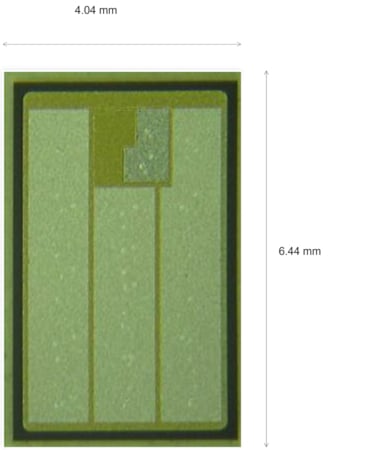

Les puces nues sont physiquement fragiles. Des forces déséquilibrées lors de la fixation peuvent facilement provoquer des fissures ou des éclats. De plus, la petite taille de la puce—souvent inférieure à 5 mm d’un côté—rend la manipulation encore plus difficile. En outre, les puces nues peuvent se rompre en raison de pics de tension causés par la rapide variation du courant (di/dt) du signal de test, combinée à l’inductance parasite environnante.

La seule méthode actuellement utilisée pour caractériser une puce nue consiste à créer une carte de test Double Pulse Test (DPT) complète pour la puce. Cette carte comprend une PCA intégrée avec des pilotes de porte, des condensateurs de banque, des composants d’isolation et d’autres éléments nécessaires. La puce est soudée à la PCA du côté drain, et un fil de liaison est utilisé pour établir des connexions avec la source et la porte. Souvent, la puce est recouverte d’un matériau isolant.

Figure 1. Exemple de puce nue. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF] et Wolfspeed.

Cependant, cette configuration n’est utilisée qu’une seule fois pour la caractérisation de la puce car la PCB ne peut pas être réutilisée. Les coûts associés, le temps, l’effort et le manque de réutilisabilité découragent les ingénieurs de l’utiliser fréquemment.

Technologie permettant la caractérisation dynamique des puces nues

Il existe quelques technologies et techniques clés nécessaires pour permettre la caractérisation dynamique d’une puce nue. Créer un support spécial pour une puce nue est le principal aspect de la solution. Ce support spécial doit répondre aux exigences suivantes :

- Aucune aiguille de sondage pour éviter les effets parasites supplémentaires et le risque d’arc électrique

- Le support doit entrer en contact avec la structure verticale de la puce nue

- Le contact avec la puce nue doit être suffisamment serré pour assurer la conductivité électrique, mais pas trop serré pour éviter les fissures physiques ou les éclats

- Contact sans soudure

- Un mécanisme d’alignement d’une petite puce nue avec les électrodes du support de test

- Minimiser les effets parasites dans le support de test (par exemple,

- Le support doit avoir des capacités de haute tension et de haut courant (par exemple, 600V et 40A)

- Manipuler une puce nue avec précaution est essentiel pour éviter les dommages physiques

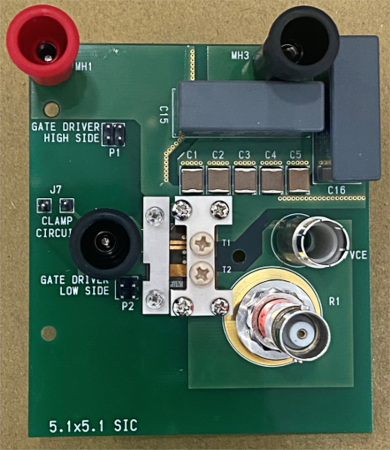

La solution décrite ci-dessous utilise des technologies nouvellement développées pour les tests dynamiques de puces et est réalisée pour des testeurs de double impulsion de dispositifs discrets. La carte DUT est assez simple, comme illustré dans la Figure 2. La même technologie peut être exploitée pour les testeurs de double impulsion de modules de puissance, permettant aux ingénieurs de modules de puissance de l’utiliser pour caractériser les puces nues et les modules de puissance avec cette nouvelle solution.

Figure 2. Exemple de carte DUT PD1500A pour la caractérisation dynamique d’une puce nue. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Sur la carte DUT, des traitements spéciaux sont appliqués aux électrodes de la PCB pour permettre un contact sans soudure. Une PCB flexible avec un traitement d’électrode similaire est également utilisée pour les connexions supérieures. En plaçant une puce entre la PCB principale et la PCB flexible, il devient possible de faire circuler le courant du haut de la puce vers le bas, permettant ainsi des mesures de courant pour les dispositifs à structure verticale.

Le design de la PCB vise à minimiser l’inductance parasite dans les boucles de puissance et de porte. Le support comporte des broches multiples soigneusement conçues qui dépassent de la PCA, alignant ainsi précisément une puce nue pour un contact optimal avec les électrodes. L’absence d’aiguilles de sondage réduit encore l’inductance parasite dans le circuit de test.

Pour les dispositifs Si et SiC, un résistor de shunt coaxial peut être utilisé, même avec son inductance d’insertion de plusieurs nanohenrys (nH). Dans le cas des puces nues GaN (nitrure de gallium), un capteur de courant breveté [1] fournit un moyen supplémentaire de minimiser l’inductance parasite. Les puces nues de semi-conducteurs de puissance présentent généralement différents facteurs de forme. Notre stratégie consiste donc à créer une carte DUT sur mesure pour les PD1500A et PD1550A de Keysight, comme illustré dans la Figure 3.

Figure 3. Support DUT de puce nue personnalisé pour PD1500A/PD1550A. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

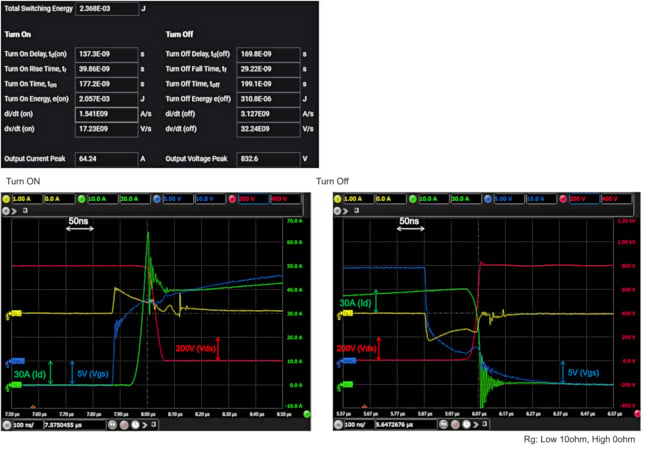

La Figure 4 montre des exemples de résultats de mesure obtenus pour une puce nue de MOSFET SiC avec une tension nominale de 1,2 kV. Le test est effectué à 800 V et 40 A, démontrant que le support offre une capacité de tension et de courant suffisante pour le MOSFET SiC de 1,2 kV. Les formes d’onde sont très propres, avec un léger dépassement de tension Vds à l’extinction. L’inductance de boucle de puissance calculée à partir de la forme d’onde de mise sous tension n’est que de 8,3 nH.

Figure 4. Résultats du test (mise sous tension & extinction) pour un MOSFET SiC. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Le support pour les puces nues peut être facilement utilisé avec des traceurs de courbe, supprimant ainsi le besoin d’un prober de wafer pour les mesures statiques des puces nues et améliorant considérablement la productivité.

La caractérisation dynamique des puces nues, jadis considérée comme difficile et presque impossible à réaliser, est désormais accessible grâce à des solutions nouvellement développées pour les testeurs de double impulsion de la série PD1500 de Keysight, offrant une solution sur mesure pour les puces nues.

Cet article est initialement paru dans Bodo’s Power Systems [PDF] à coécrit par Ryo Takeda, Yu Watanabe et Takamasa Arai de Keysight Technologies.